競爭力

Competitive power

瑞波光電創(chuàng)新團隊專注于半導(dǎo)體激光芯片領(lǐng)域,傾力研發(fā)具有高性能、高可靠性的一流品質(zhì)的大功率半導(dǎo)體激光芯片。團隊擁有多名資深設(shè)計和工藝專家,具備數(shù)十年的專業(yè)開發(fā)和生產(chǎn)經(jīng)驗,我們在運用專業(yè)態(tài)度與設(shè)計制造能力打造產(chǎn)品的同時,也將滿腔熱忱傾注于其中。 瑞波光電創(chuàng)新團隊專注研發(fā)大功率激光芯片,同時也針對封裝、測試等特定需求,提供客制化解決方案我們的芯片,經(jīng)過嚴苛的性能測試和老化測試,達到世界一流水平。

將集設(shè)計和制作技術(shù)于一體,尤其

在保證芯片可靠性的制造工藝方面具備重大優(yōu)勢。

1)芯片設(shè)計方面,公司在外延結(jié)構(gòu)設(shè)計和芯片設(shè)計方面,創(chuàng)新采用非對稱波導(dǎo)結(jié)構(gòu)設(shè)計、量子阱結(jié)構(gòu)優(yōu)化等新技術(shù),有效降低量子阱激光器的閾值電流密度,降低端面光功率密度,提升產(chǎn)品的性能和可靠性。

2)芯片制造方面,在已掌握關(guān)鍵技術(shù)基礎(chǔ)上,通過創(chuàng)新的光刻/刻蝕/蒸鍍技術(shù)、量子阱失序技術(shù)、光柵制備技術(shù)、非泵浦窗技術(shù)、腔面鈍化和光學(xué)鍍膜技術(shù)、封裝工藝技術(shù)等,提高產(chǎn)品的性能。同時,不斷運用自動化、智能化、數(shù)字化技術(shù),提升產(chǎn)線效率,降低成本,改善良率。

3)芯片測試表征方面,團隊建立完整的測試表征方法,包括器件性能測試、老化和壽命測試、器件失效分析等,并開發(fā)系列表征測試設(shè)備,為芯片研發(fā)及生產(chǎn)提供了強有力的保障。

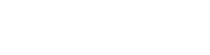

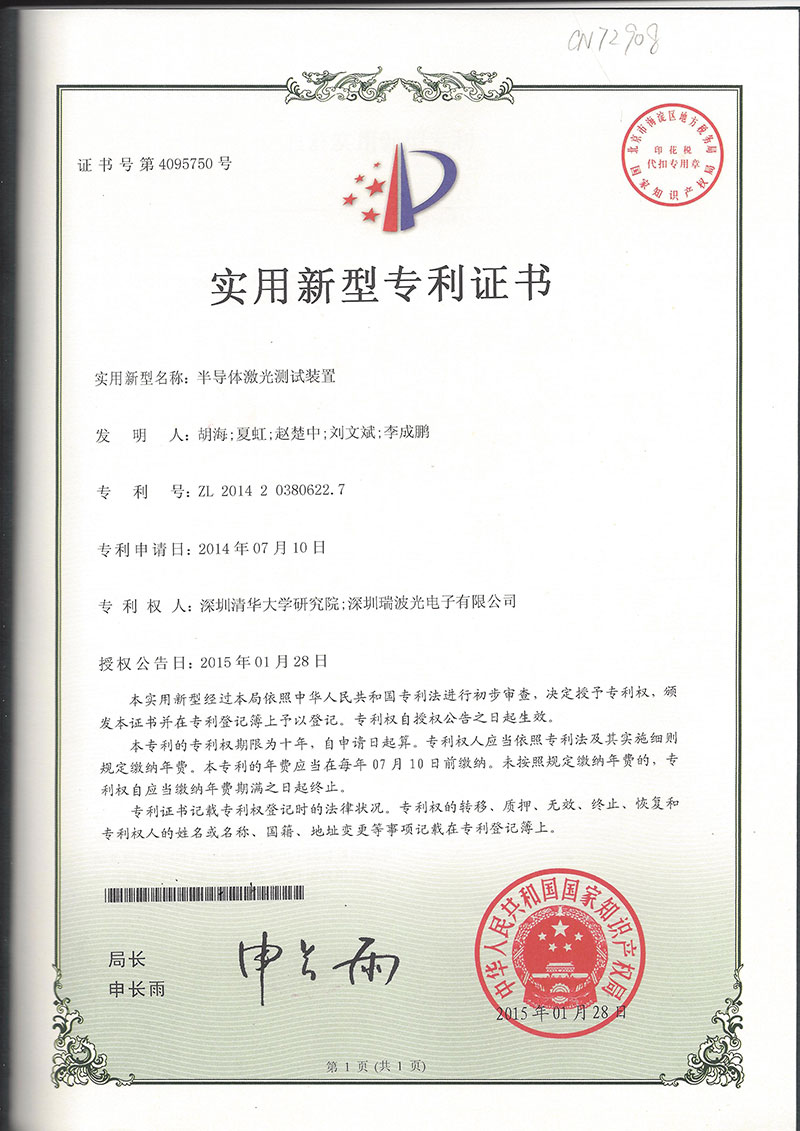

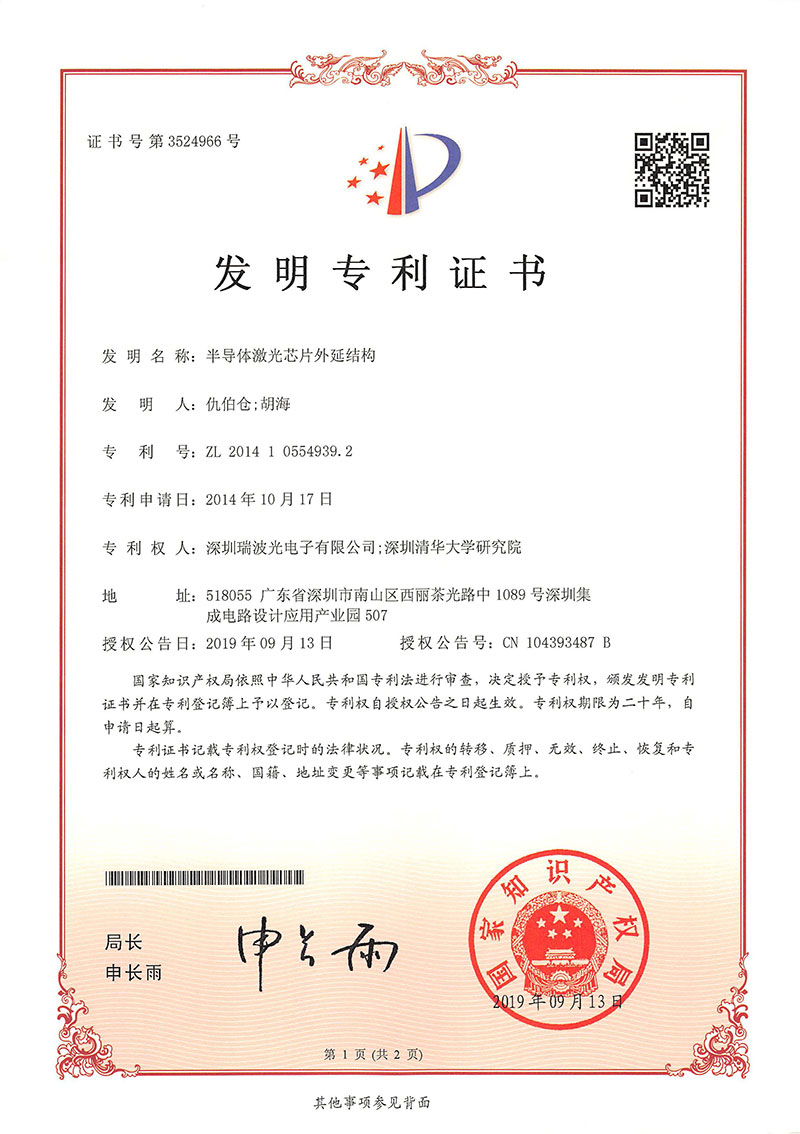

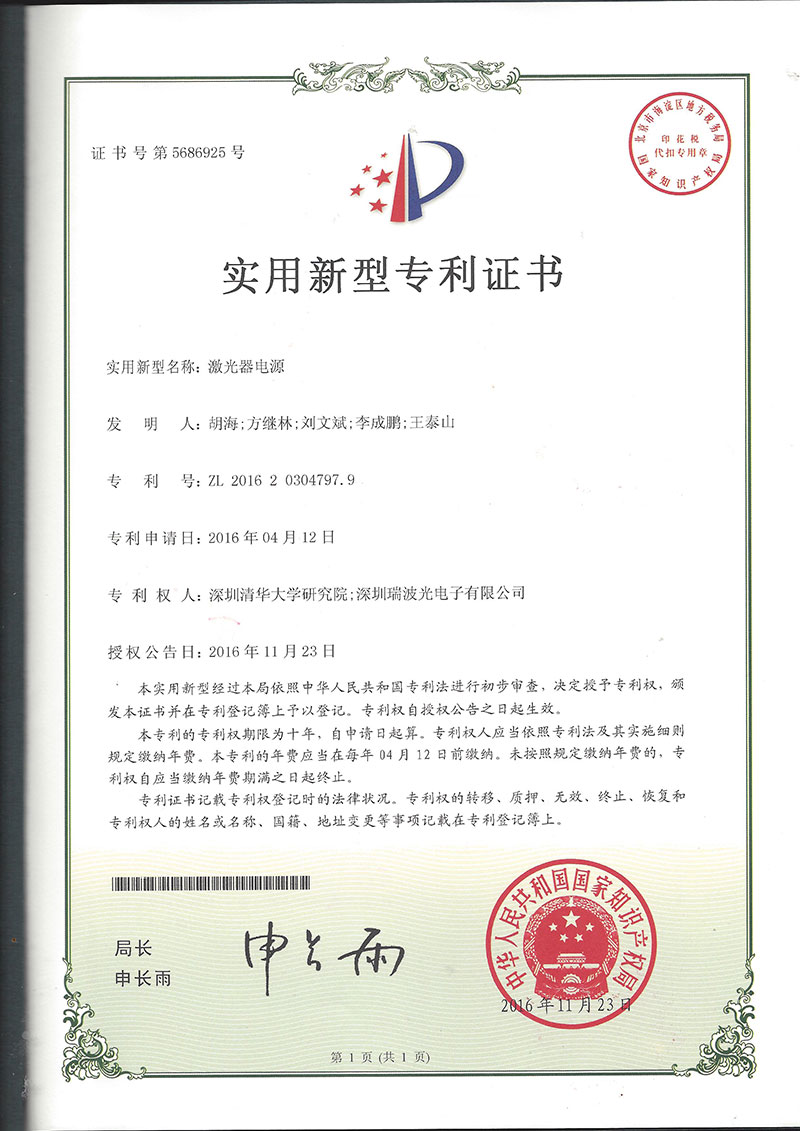

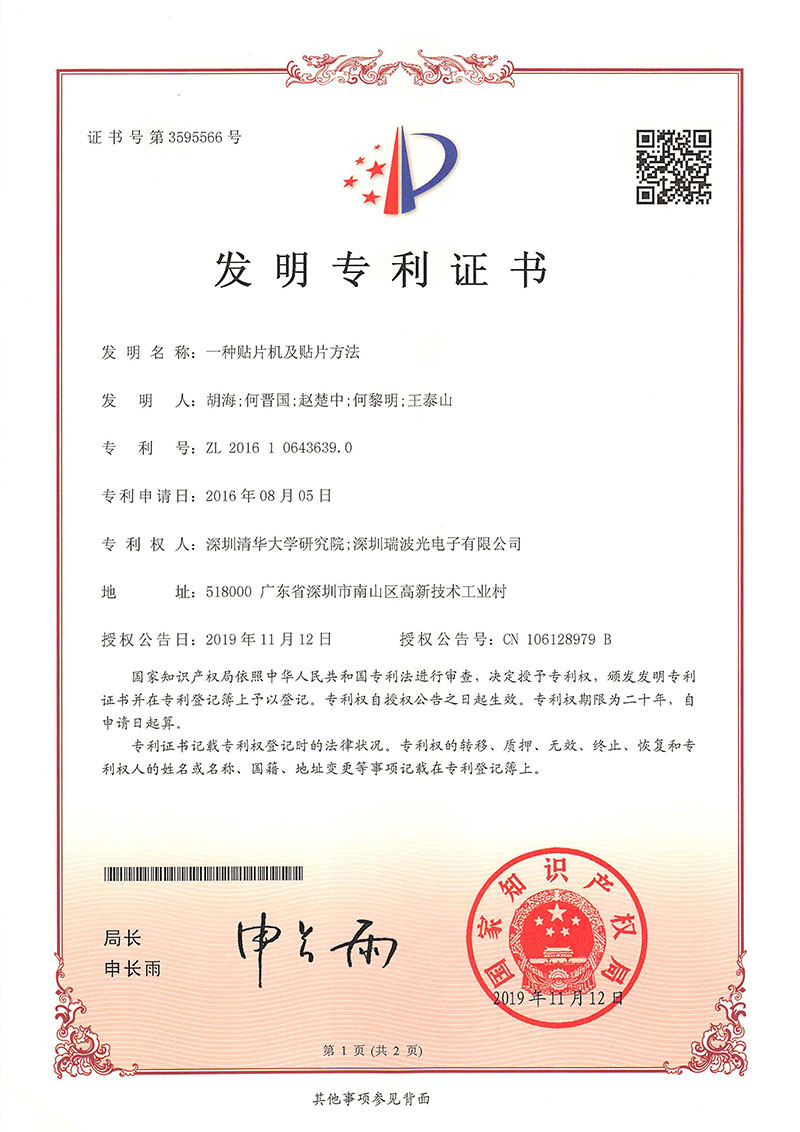

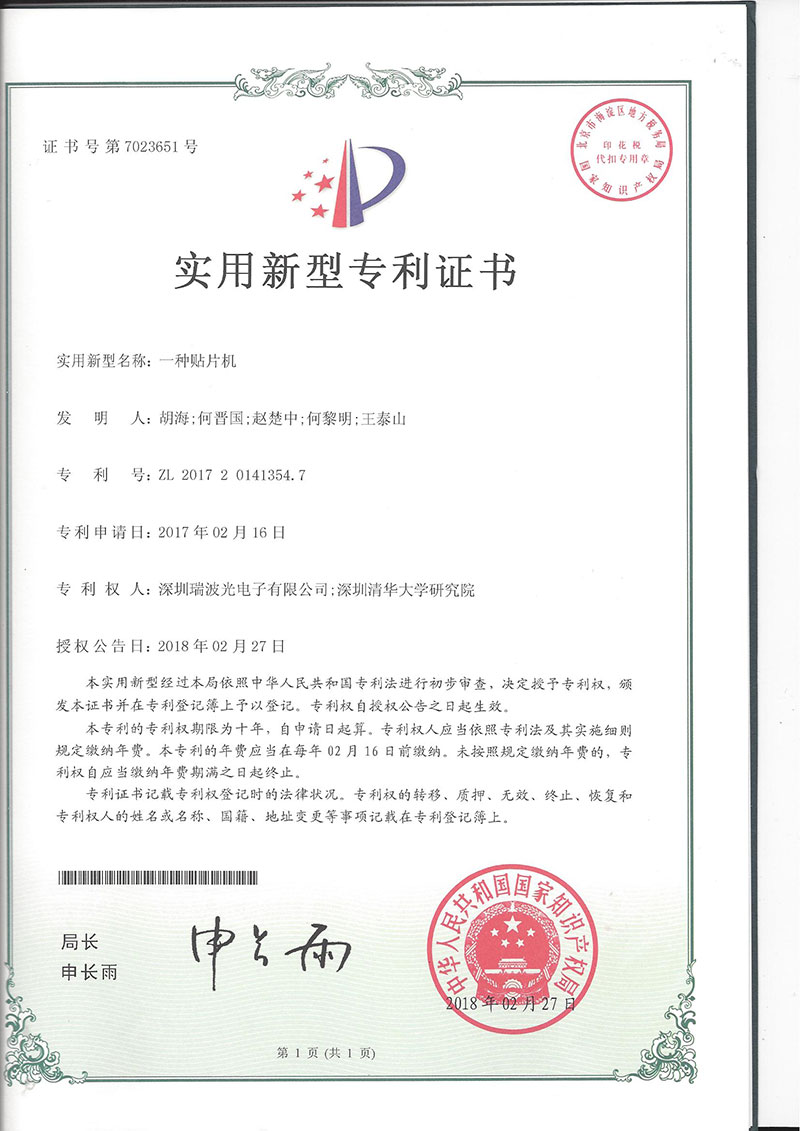

專利

Patent

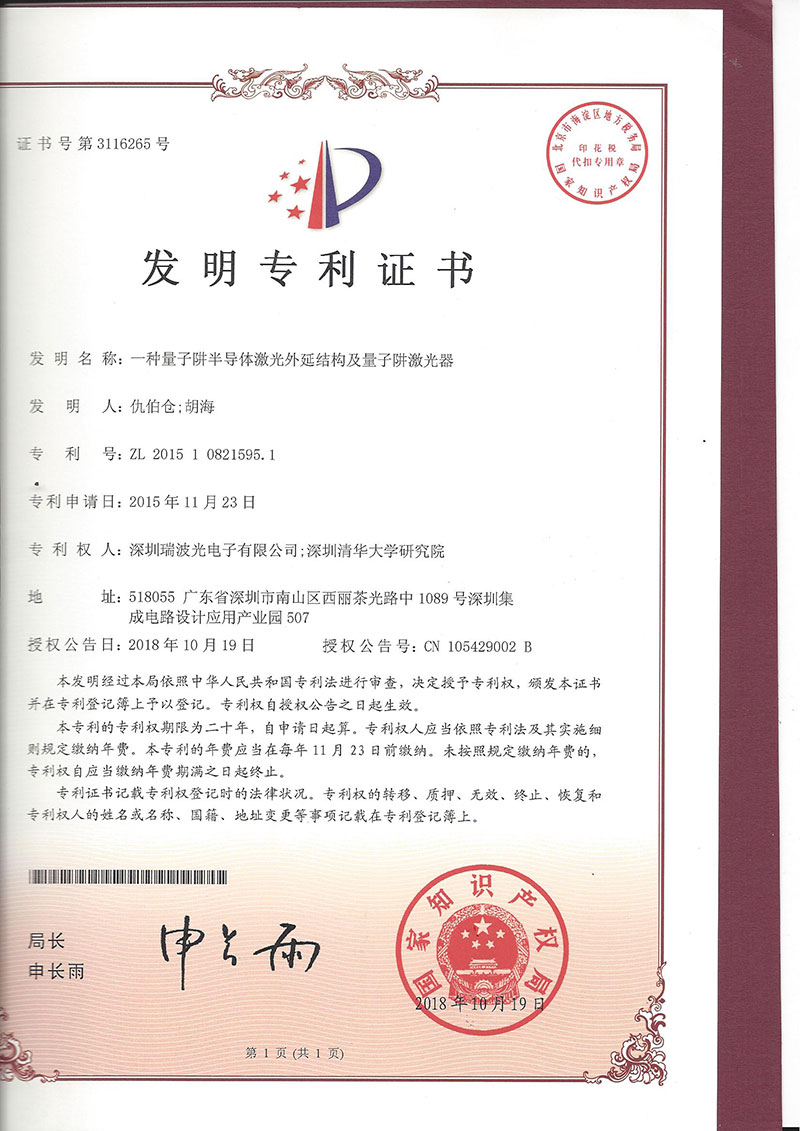

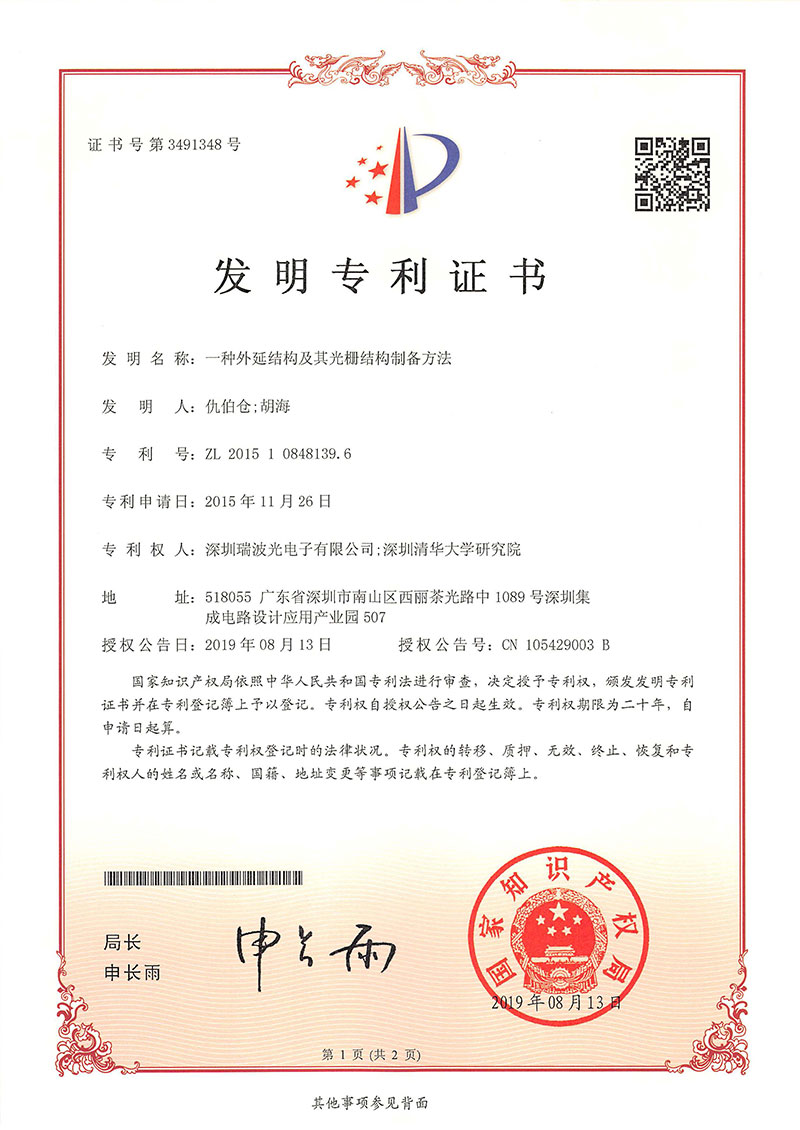

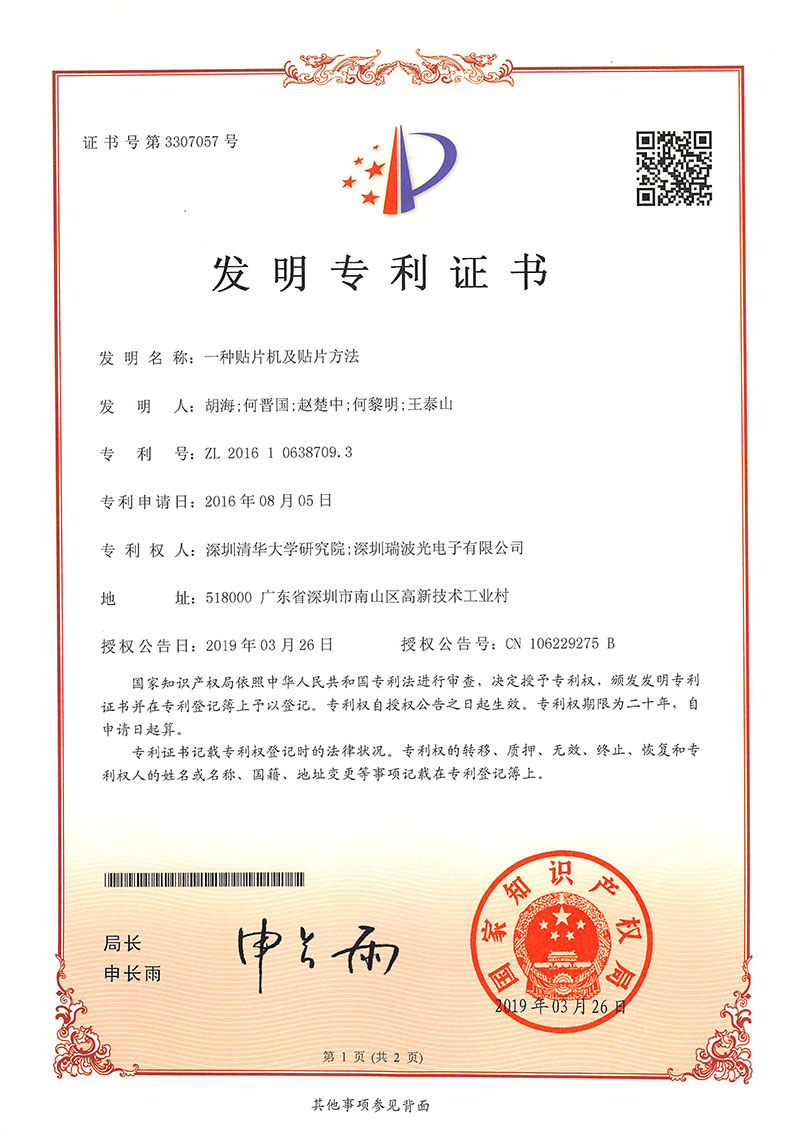

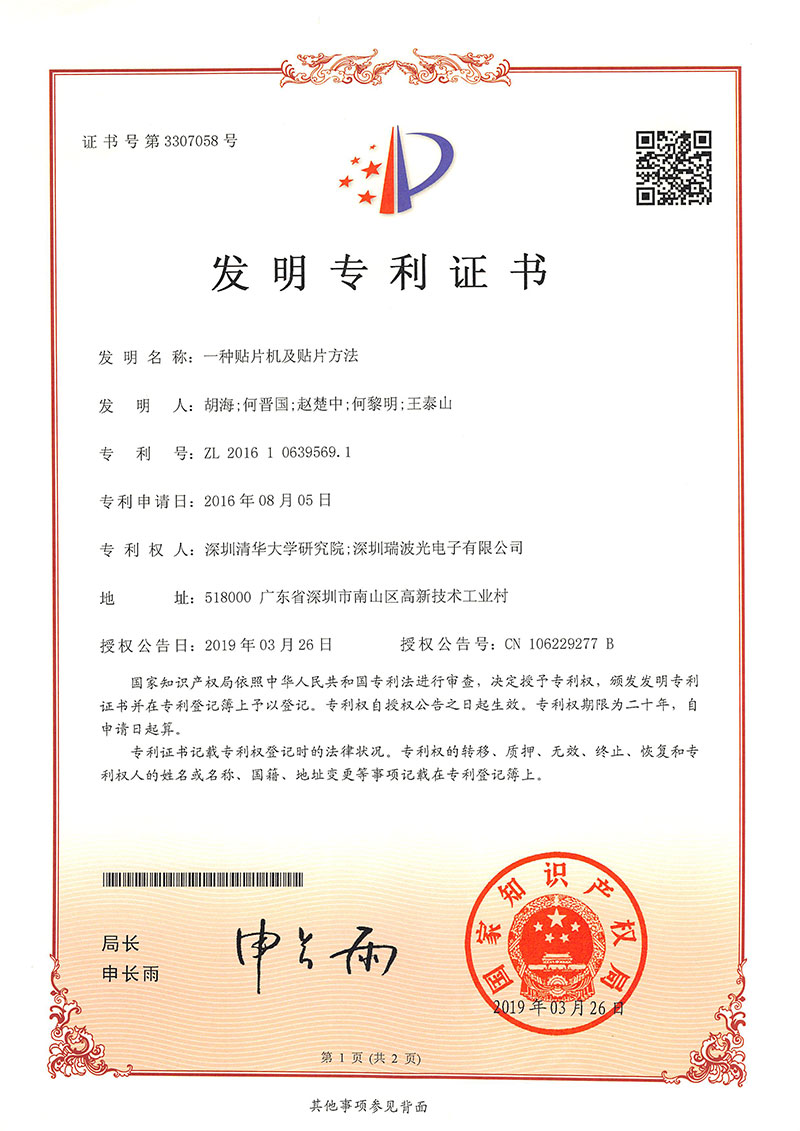

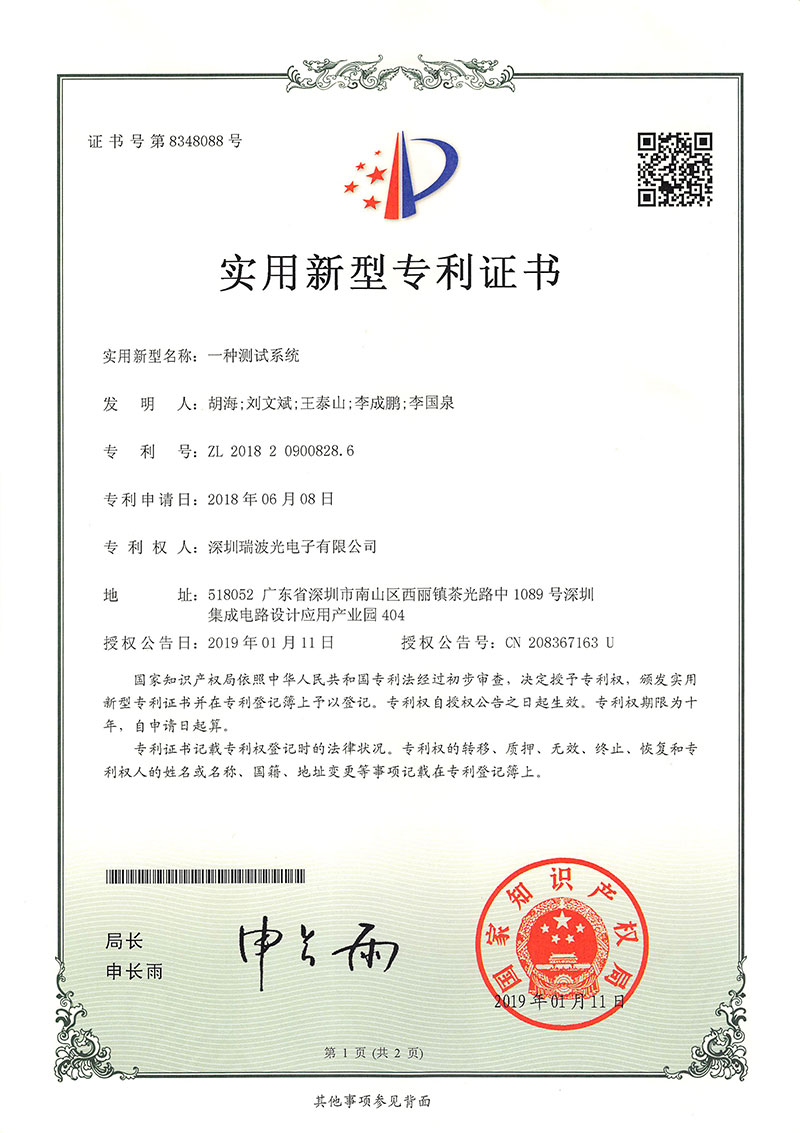

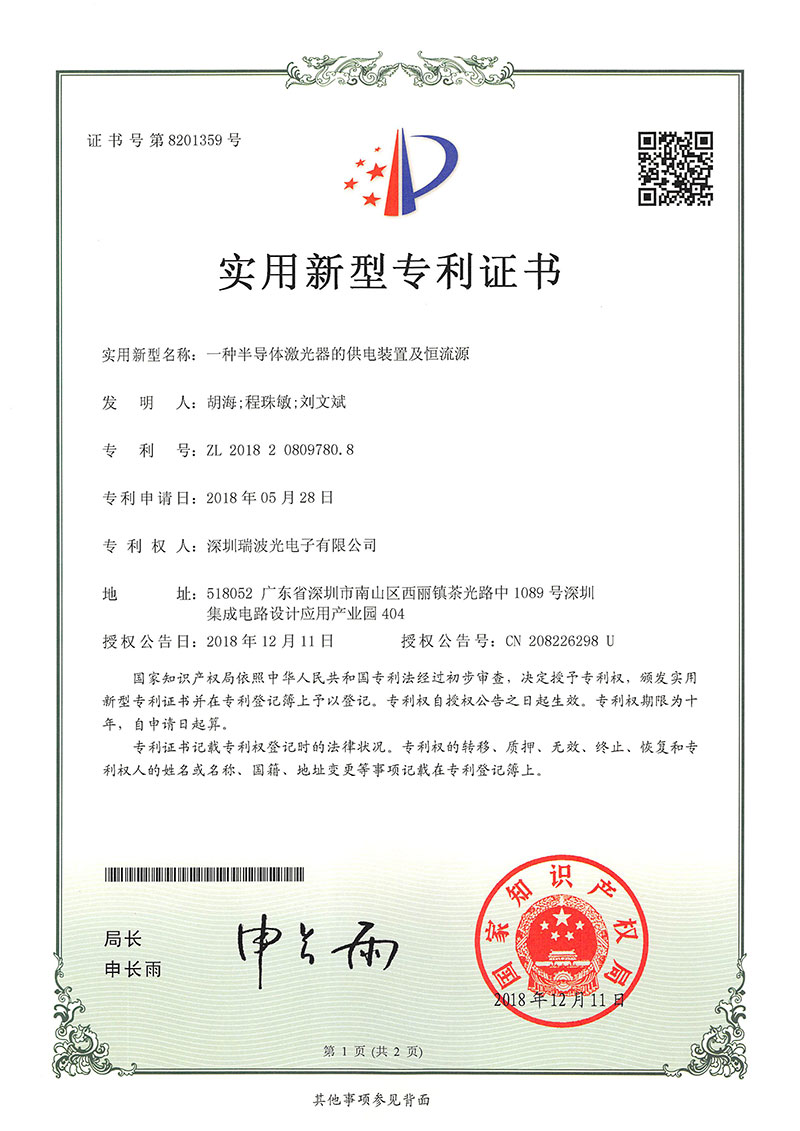

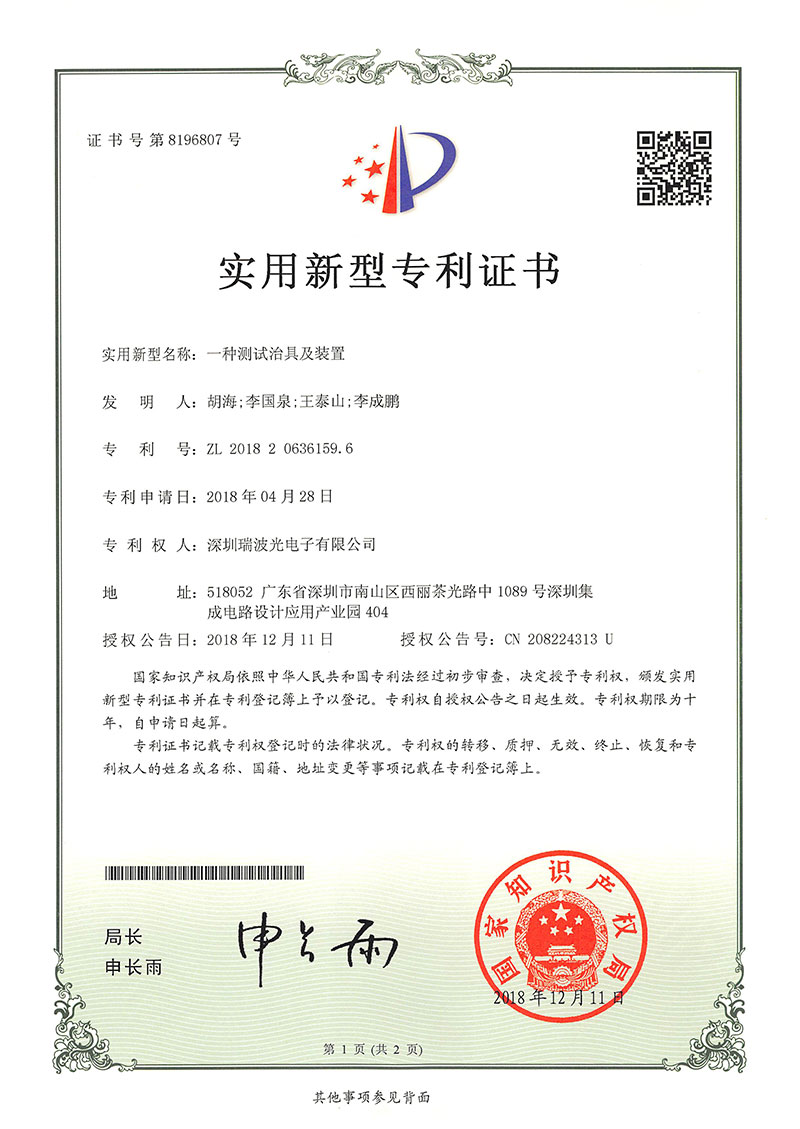

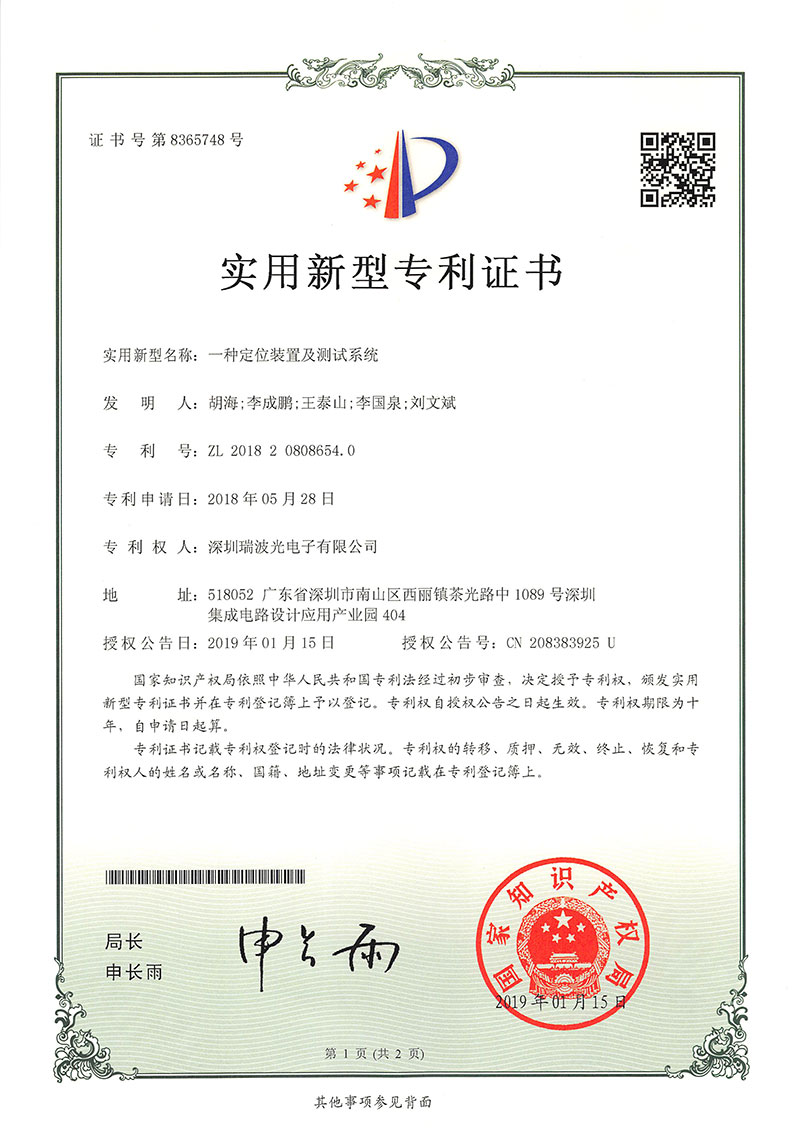

瑞波光電在研制大功率半導(dǎo)體激光芯片的過程中,一直秉承擁有自主知識產(chǎn)權(quán)和核心專利的理念,積極布局專利申請。累計提交了87件知識產(chǎn)權(quán)申請,其中發(fā)明專利46件,實用新型27件,PCT專利9件,軟著5件;已授權(quán)46件,其中發(fā)明17件,實用新型24件,軟著5件。發(fā)表與項目研究內(nèi)容相關(guān)的論文23篇。

申請專利

發(fā)明專利

PCT

新型專利

軟件著作權(quán)

質(zhì)量

Quality

瑞波光電質(zhì)量方針

“客戶為本,技術(shù)領(lǐng)先?,品質(zhì)卓越,持續(xù)改進”

客戶為本

每一項決策為客戶創(chuàng)造價值,每一次交貨讓客戶滿意。

品質(zhì)卓越

每一項行動以品質(zhì)為第一,每一次交付追求零缺陷。

技術(shù)領(lǐng)先

不斷創(chuàng)新,樹立行業(yè)領(lǐng)先的品牌,快速響應(yīng)并超越客戶的需求。

持續(xù)改進

不斷改進我們的產(chǎn)品、流程和服務(wù),每一次改進爭取精益求精。